这是一篇电子信息硕士论文代写范文,信号处理;MTCA;高级夹层卡;Zynq;低电平射频控制系统;核科学技术;电信技术;自动化技术为研究论点。本文主要对粒子物理实验装置中的通用 LLRF 控制系统的关键技术进行研究,AMC板卡的规范性设计和丰富的可拓展性让该板卡能够应用于不同粒子物理实验装置中。

目录

摘要

abstract

1.绪论

1.1 课题背景

近年来,核物理实验技术的跨越式发展,使离子束轰击原子核的研究手段成为揭示原子核结构与动态演化规律的核心途径。中国散裂中子源(China Spallation NeutronSource,CSNS)作为全球四大大型加速器装置之一[1],是物质科学、生命科学等领域原始创新的关键平台。CSNS 的核心运行依赖于高精度的粒子加速与控制技术——通过负氢离子束的多级加速、质子束轰击钨靶产生中子[2],其束流中的能量、稳定度、发射度等品质系数的优劣,直接决定实验精度。在加速器粒子实验过程中,微波场梯度通常高达 10MV/m 量级,无法直接调控,需通过低电平射频(Low Level Radio Frequency,LLRF)控制系统对微波信号的幅度与相位进行精确控制。LLRF 控制系统作为加速器的核心系统,其控制性能是束流品质的决定性因素。然而,传统加速器控制板卡受限于数据传输速率、处理能力及功能扩展性[4],在面对 CSNS 等高能量、高束流强度装置时,传统板卡的数据吞吐量不足与微秒量级响应时长,使得束流参数实时反馈失效,难以满足能量稳定度与相位控制精度的严苛要求,并且功能固化的硬件设计无法适应多样化实验需求[5][6]。微电信计算架构(Micro Telecommunications Computing Architecture,MTCA)架构的出现为上述难题提供了变革性解决方案。作为 PCI 工业计算机制造商协会(PICMG)定义的标准化开放架构,MTCA 继承了 AdvancedTCA 的高性能特性,兼具高密度集成、模块化设计与灵活扩展能力,其核心载体高级夹层卡(Advanced Mezzanine Card,AMC)板卡具备高速数据处理能力、柔性功能重构、紧凑化系统集成三大技术优势,精准匹配加速器控制需求[7][9]。CSNS 直线加速器机柜空间仅为传统机柜的 1/3[10],对新一代加速器的 LLRF 控制系统提出了更高的要求[11]。本课题立足 CSNS 实验实际需求,针对现有控制板卡在性能与架构上的双重局限,提出基于 MTCA 平台的高集成度 AMC 数字信号处理板卡设计方案。通过融合异构多核处理器 Zynq7000 与高速接口技术,达成硬件模块化、软件可编程、功能可重构的突破,为新一代加速器 LLRF 控制系统提供高性能、易扩展、强适配的核心硬件载体。研究成果不仅支撑我国高能物理实验的前沿探索,更将为工业加速器、医疗设备等领域的国产化控制技术提供共性平台。

1.2 国内外研究现状

1.2.1 大型加速器设施中 LLRF 控制系统发展现状在粒子物理研究向微观尺度不断深入的进程中,大型加速器对束流品质中的能量稳定性、相位精度、发射度等品质系数的要求持续提升,推动 LLRF 控制系统使用的架构从旧的 VEM、CPCI、ATCA 架构逐渐转变为 MTCA 架构,其中使用的信号处理板从分离式逐渐转变为集成的标准 AMC 板卡。以下从国内外典型案例展开分析:(1)日本质子加速器研究中心(Japan Proton Accelerator Research Complex,J-PARC)在其环形质子同步加速器的 LLRF 升级中,采用 MTCA.4 架构构建分布式控制平台,核心处理单元选用 Xilinx Zynq UltraScale+ RF SoC,集成 14 位 1GSps ADC 与 14 位 6.4GSpsDAC,实现 S 波段射频信号直接采样与数字下变频处理[12]。该系统通过 FPGA 逻辑实现三阶数字预失真算法,将速调管非线性失真抑制至-80dBc 以下,多腔体协同控制延迟优化至 0.8μs,但其硬件成本较高,且未针对紧凑型机柜部署优化[13]。(2)南非加速器基科学实验室(iThemba Laboratory for Accelerator Based Sciences,iThemba LABs)针对 MTCA 架构的实时性与扩展性进行优化,其 LLRF 系统采用模块化设计,集成 8 通道 16 位 125MS/s ADC/DAC,支持多通道同步采样与高频信号处理。通过引入 RapidIO 3.0 总线,板间数据吞吐量提升至 50GB/s,满足高速束流数据的实时交互需求[14]。但其需额外配置专用 RapidIO 交换 AMC 模块,导致单套系统硬件成本增加 30%,且多模块堆叠使单机箱仅能容纳 6 套 LLRF 控制单元,难以适配紧凑型机柜部署场景。系统搭载直接数字频率合成技术,在 100kW 功率工况下,实现幅度/相位控制精度稳定在 0.008%/0.008 度,并将高频段相位噪声抑制至-125dBc/Hz,达到高精度射频控制标准。在稳定性设计方面,MTCA 背板嵌入独立电源隔离模块以降低噪声干扰,结合双倍路径电缆温漂补偿技术,使系统 24 小时相位稳定性提升至 0.005 度,显著优化了长时间运行的可靠性[15],其中电缆温漂补偿需依赖外部精密温控设备,增加了系统部署复杂度与运维成本。(3)中国科学院近代物理研究所(HIRFL)持续优化高级电信计算架构(AdvancedTelecommunications Computing Architecture,ATCA)架构。该系统采用 Xilinx VersalPremium 自适应计算加速平台,实现 5.5MHz~54MHz 宽频信号实时处理,支持多频段射频信号的动态调谐与高精度控制。在数据交互方面,系统通过 PCIe Gen4 x16 接口与CXL 2.0 协议,将前馈补偿算法对 60mA 束流负载的响应时间压缩至 50μs,显著提升了束流稳定性控制的实时性[16]。但其设计在实际使用中还面临着架构兼容性局限、核心器件依赖进口、协议适配度复杂的问题。

1.2.2 MTCA 架构的研究现状目前国内外学者围绕 MTCA 平台在加速器与核聚变诊断系统中的应用展开,涵盖LLRF 控制系统、图像与信号采集、数据处理、算法优化等多个方面。Li 等人[17]聚焦于合肥先进光源(HALF)线性加速器(LINAC)中基于 MTCA.4 架构的低电平射频(LLRF)原型系统。该系统通过非 IQ 采样技术配合数字滤波器抑制奇次谐波,获得约 73dB 的信噪比(SNR),并采用开环幅度控制与闭环相位控制相结合的策略,实现了在饱和功率源下稳定的相位控制。Pietrzak P.等人[18]开展了基于 MTCA.4架构的图像采集系统延迟评估研究,用于聚变实验中的实时等离子体诊断。其系统支持多种摄像头接口,并通过两种测量方法验证了系统在 ITER 诊断要求的延迟范围内的性能表现。Zhang 等人[19]设计了一种用于 EAST 装置的中子能谱实时诊断系统,其基于MTCA 架构开发,具备 FPGA 实时数据处理能力,可应对高达 2Mcps 的计数率要求,并实现了对中子与伽马射线的实时信号采集和处理。Wang 等人[20]开发了用于 CSNS-II和 SAPS-TP 项目的通用控制与数据采集 AMC 模块。该模块基于 MTCA.4 标准,核心处理单元为 Xilinx Zynq 7045 SoC,具备丰富的模拟/数字接口资源,支持多种加速器子系统的控制与数据处理需求。Qiang 等人[21]针对 EAST 装置中快中子谱实验,设计了高速数字脉冲采集与处理系统,解决了高计数率下传统核电子线路难以处理的问题。该系统基于 MTCA 架构,支持 PCIe 通信,满足高带宽、高精度的实时分析需求。谢春杰等人[22]针对 S 波段直线加速器的数字低电平系统展开研究,采用 IQ 解调与 CORDIC 算法进行 PI 闭环控制,并通过国产芯片和光口通信增强系统的稳定性和抗干扰能力,实现在束流实验中优于 0.1°的相位稳定度。李林等人[23]针对上海软 X 射线自由电子激光装置(SXFEL)C 波段前端射频板性能进行了测试与研究。基于 MTCA 平台设计的DWC8VM1 板卡表现出优异的隔离度、幅相稳定性和低附加相位噪声,满足国际先进低电平控制系统的性能要求。Miguel 等人[24]将一维卷积神经网络(1DCNN)应用于基于FPGA 的 MTCA 数据采集平台中,进行中子与伽马波形实时分类。该研究借助 Open CL环境简化网络架构设计与优化,实现了实时脉冲形状判别任务。

1.3 本文研究内容及结构安排

1.3.1 本文研究内容加速器设施中的低电平射频(LLRF)控制系统普遍面临一系列核心技术瓶颈,如高功率非线性效应处理不足引发的束流能量漂移、极端工况下的动态响应滞后导致场强稳定性下降、多物理场耦合的自适应补偿机制缺失而过度依赖人工干预,以及关键控制芯片受限于进口壁垒等问题,严重制约了加速器系统的长期运行稳定性与可维护性。针对上述挑战,本文结合中国散裂中子源(CSNS)二期工程的实际需求,设计并实现了一款基于 MTCA.4 架构、符合 AMC 标准的国产化数字信号处理板卡。

硬件部分以 Xilinx Zynq-7045 SoC 为核心处理器,构建“ARM Cortex-A9 处理器+FPGA 可编程逻辑”异构多核协同平台。PS 端采用双核 800 MHz 处理器,负责系统启动、通信协议解析与状态监测,支持毫秒级对加速腔体谐振频率、增益等参数进行配置更新;PL 端集成 125K 逻辑单元与 8 通道 GTX 高速串行收发器,支持 250 MHz 内部逻辑运行频率,单通道处理链延迟低于 10 ns,满足对纳秒级射频反馈精度的工程要求。在模拟前端方面,采用 4 片 AD9268 构建 8 通道同步采样链路,具备 125 Msps 采样速率、16 位分辨率与 650 MHz 模拟带宽。前端输入支持通过开关网络实现 AC/DC 耦合切换,灵活适配 3 MHz 至 650 MHz 宽频射频信号采集。输出通道选用 AD9783 作为核心 DAC,具备 500 Msps 速率与内置四象限调制能力,结合 FPGA 内部数字预失真算法,实测无杂散动态范围(SFDR)提升至 85 dBc 以上,有效抑制高次谐波及非线性失真。为保障信号完整性与系统稳定性,电源系统设计采用三级滤波结构:输入端配置共模电感屏蔽高频干扰,中间段 LDO 提供 1.8 V/3.3 V 低噪声稳定电压,输出端通过片间分布式去耦实现对核心器件的局部电源稳定补偿。时钟系统以 Si5394J 为核心,构建支持多源输入、低相位噪声、高可靠性的时钟网络,输出 125 MHz ADC 采样时钟与 250MHz 系统时钟信号,配合 LTC6950 分配器实现跨域同步与多模块一致性驱动,时钟路径布线独立于 16 层 PCB 结构中单独隔离,显著降低系统级抖动和干扰耦合。在软件架构方面,系统围绕 Zynq 异构平台构建分层协同机制。PS 端运行裁剪型PetaLinux 系统,内核支持 I²C、SPI、AXI-DMA、USB、Ethernet 等外设驱动,支持从TF 卡、QSPI Flash 等介质启动。PS 用户层部署配置服务、数据上传、状态监测和日志管理多线程服务模块,并集成 EPICS IOC 通信接口,实现与主控系统的无缝数据与控制联动。支持裸板模式下独立运行,无需 MCH 集中控制,实现 MCH 失效下的系统自主启动与在线调试,相比传统架构调试效率提升 50%以上。PL 端以 Verilog HDL 进行编程,实现高速数据处理链路,构建包括光纤接口协议栈、PCIe DMA 传输控制器、跨时钟域交互逻辑与时钟配置子系统四大处理模块。光纤通信模块基于 GTX 硬核收发器实现高速串行数据解析与时钟恢复功能;PCIe 模块支持DMA 直连与 AXI 桥接双模式,灵活适配高速数据与控制命令通道;跨域交互模块通过异步 FIFO 与握手机制解决 125 MHz 采样域与 250 MHz 处理域之间的时序不一致问题,确保数据同步精度优于 5 个时钟周期;时钟配置模块通过 SPI 与 LTC6950 通信,可实现主备时钟源自动切换与工作状态实时监测。综上所述,本文从硬件平台构建、采样链路优化、信号完整性控制、软硬件交互逻辑设计等多维度出发,构建了一套高集成度、高稳定性、高自主性的 LLRF 数字信号处理板卡系统,突破了目前加速器控制系统在高速数据交互、多域异步处理与国产化适配方面的瓶颈,验证了在实际工程条件下的功能完整性与链路稳定性,为下一代国产加速器控制平台的落地提供了可复制的技术方案。

1.3.2 本文结构安排第 1 章绪论。本章围绕课题背景展开,阐述大型加速器 LLRF 控制系统对高性能硬件平台的需求,分析国内外在 LLRF 技术、MTCA 架构及 AMC 板卡领域的研究现状,指出现有设计的不足。明确本文以 AMC 信号处理板为研究对象,聚焦硬件架构设计、软件协同机制及系统测试,旨在构建适配 LLRF 控制需求的高性能模块。第 2 章相关理论基础。本章系统梳理 LLRF 控制系统原理,阐明其通过 ADC 采样、数字处理、反馈控制实现射频场稳幅稳相的闭环机制;解析 MTCA 架构的标准化背板、机箱结构及核心模块,揭示其在高速互联、模块化集成中的优势;介绍 AMC 板卡的协议规范、功能分类及接口设计,凸显其在异构计算与灵活扩展中的作用。三者共同构成硬件设计的理论支撑,为后续模块选型与电路设计提供依据。第 3 章信号处理板硬件设计。本章以 LLRF 控制需求为导向,设计基于 Zynq-7000SoC 的 AMC 板卡硬件架构。核心器件选型兼顾性能与适配性,如 AD9268/AD9783 保障高精度模数转换,Si5394/LTC6950 构建低抖动时钟网络。具体电路设计涵盖电源分级转换、多源时钟树、高速接口及智能管理模块,解决高速信号完整性、时序控制及可靠性问题。第 4 章信号处理板软件设计。本章依托 Zynq 异构架构,构建“PS 端系统管理+PL端实时处理”的软件体系。PS 端通过 PetaLinux 实现任务调度、EPICSIOC 远程控制及设备驱动,PL 端以 Verilog 实现 DDC 数字下变频、AXI-Stream 数据搬运,支持参数动态重构。,信接口融合以太网与 USB 串口,兼顾远程控制时效性与本地调试便利性,实现软硬件深度协同。第 5 章系统测试。本章通过频谱性能测试验证 ADC/DAC 的动态范围与频率响应,确认 DDC 算法的幅相计算精度;光纤模块测试实现 10Gbps 高速数据传输;PCIe 模块验证 5Gbps 稳定通信,满足 LLRF 系统对数据吞吐量与可靠性的要求。测试结果表明,板卡关键性能指标达标,为工程应用提供数据支撑。第 6 章总结与展望。本章总结设计成果,指出 AMC 板卡通过软硬件协同实现了高精度信号处理、多模式适配及可靠通信,满足 LLRF 控制需求。展望未来研究方向,提出进一步优化集成度、引入 AI 算法提升自适应控制能力、拓展多板协同处理架构,为下一代加速器测控模块设计提供思路,推动相关技术在高端装备领域的深化应用。

2.相关理论基础

2.1 LLRF控制系统原理

整个系统以 Linux 主控计算机作为高层控制中心,运行控制软件用于设定射频场的目标幅度和相位等参数,并监视系统状态[40]。Linux 主控系统通过高速 PCIe 接口与下位机数字控制硬件通信[40],读写 FPGA 上的寄存器,实现对 LLRF 各模块的配置控制和数据读出。这一架构确保上位机能够实时下达控制指令并获取测量数据,为射频场稳定提供了人机接口和监控平台。实际射频信号的高速处理由 FPGA 等数字硬件承担,Linux主控通过 PCIe 总线对其进行管理协调。在信号流程方面,LLRF 系统从加速器射频腔体或功放输出提取取样信号,经由前端射频链路送入模数转换与采样模块。该模块包含高速模数转换器(ADC)[41],将射频模拟信号数字化。为了捕获射频腔的瞬时场信息,ADC 以高采样率对射频取样信号进行采样,输出对应的数字序列。采集到的原始数字射频数据首先进入预处理模块,在此阶段对数据进行初步的数字信号处理。经过预处理后的数字信号再送入数字下变频(DDC)[42]模块进行频带平移,即 I/Q 解调处理。数字下变频通常通过将 ADC 采样得到的数字射频信号与内部产生的本振参考正交信号相乘,实现将高频射频信号转换到零中频基带,从而得到正交的同相分量 I 和正交分量 Q。经过 DDC 后得到的 I/Q 数据仍按射频采样时序排列,但已包含了原射频信号的幅度和相位信息而不再包含载频。

2.2 MTCA架构原理

MTCA 架构的核心优势源于其标准化背板设计,集成了 PCI Express、RapidIO 等高速串行总线,构建了低延迟、高可靠的数据传输网络。在 LLRF 系统中,该背板实现三大核心功能:1.多模块电气互联为处理器卡、交换卡、I/O 卡等 12 个 AMC 模块提供统一接口,支持探测器采集的射频信号实时传输至信号处理模块,同时确保控制指令以微秒级延迟下发至执行单元。2.时钟同步网络通过专用时钟接口为全系统提供抖动≤200fs 的高精度时钟信号,保障多腔体射频信号的相位一致性,这对粒子加速过程中微波场的稳定至关重要。3.总线协议适配支持 PCIe Gen2 x4、RapidIO 3.0 等协议,兼容不同功能模块的异构数据交互需求。

2.2.2 MTCA 结构MTCA 机箱作为物理载体,采用高密度紧凑设计,在有限空间内实现三大关键功能:1.散热与稳定性通过导流槽结构设计与冗余风扇配置,将核心芯片结温控制在 85°C以下,避免高温导致的信号漂移。在超导腔低温环境中,机箱内部温控模块与板卡散热铜柱配合,确保高速信号处理模块在-40°C~85°C工业级温度范围内稳定运行。2.电气连接标准化通过精密金手指连接器实现模块间信号无缝对接,减少线缆引入的寄生参数,保障10GHz 以上高频信号的完整性。3.空间效率优化单机箱可集成 12 个 AMC 模块,较传统分立式架构节省 50%以上机柜空间,适配CSNS 等装置的高密度部署需求。2.2.3 核心功能模块1.AMC 板卡AMC 板卡作为架构的核心执行单元,依据功能划分为三类,在 LLRF 系统中形成采集、处理、控制的闭环。信号处理型 AMC 集成 Xilinx Zynq SOC,PS 端运行实时操作系统处理协议解析与系统管理,PL 端通过 FPGA 实现数字信号处理算法,实时计算射频信号的幅度误差与相位偏差,并生成补偿指令。数据传输型 AMC 配置 QSFP 光纤接口与 FMC 子板接口,支持 8 路 ADC 采集的125MS/s 高速数据流通过 RapidIO 总线实时转发至后端存储或上位机,延迟≤500ns。专用功能型 AMC 如时钟管理板卡为全系统提供低噪声时钟,电源管理板卡实现12V 主电源到多电压域的高效转换。2.多模块控制器中枢(MCH)MCH[45]作为 MTCA 架构的核心管理单元,通过 Fabric Switch 芯片实现数据交换优化,动态分配背板总线带宽,将多腔体协同控制数据的交换延迟压缩至 1μs 级,支持 12个 AMC 模块的实时数据共享;时钟同步分配,接收外部原子钟或晶振输入的 10MHz 参考时钟,通过锁相环生成多路同步时钟,并通过差分缓冲器分配至各模块,确保全系统时钟相位偏差≤50fs;智能平台管理,通过 IPMB 总线实时监控 AMC 板卡状态,当检测到 ADC 通道噪声异常或 Zynq 结温超限时,自动触发降频保护或模块复位,保障系统容错能力。

2.3 AMC板卡原理介绍

AMC 模块作为 MTCA 系统的核心功能单元,是专为嵌入式系统与通信应用设计的高性能模块化架构,具备可扩展性强、成本低、支持热插拔及多种高速互联等优势,能够兼容 CPU、DSP、FPGA 等多种处理器体系结构,适用于工业标准或专有载板设计。其核心设计遵循 AMC.0 规范,该规范在确立统一接口与结构的同时,赋予模块低成本与功能多样化特性,显著提升系统模块化扩展与快速集成能力。2.3.1 AMC.0 协议AMC.0 规范以继承与创新为核心,首要目标是遵循并优化 PICMG 3.0 标准[47],在满足其基本要求的基础上,扩展机架级系统管理功能,突破传统机箱标准的限制。其次,规范聚焦 MTCA 系统构建需求,通过支持 IPMI 2.0 管理协议与热插拔能力,采用便于维护的模块化结构,有效提高系统可配置性、缩短开发周期并降低成本。在信号设计层面,AMC.0 采用低压差分信号(LVDS)与低引脚数互联方式,合理控制引脚总数,在节省空间的同时满足高速互联需求,其中每对 LVDS 信号线可支持至少 12.5 Gbps 的传输速率,前瞻性地适配未来高带宽应用。此外,规范支持多处理器架构协同处理,兼容CPU、NPU、DSP 等多种处理器类型,覆盖边缘节点、核心网络、数据中心等通信与嵌入式领域的多样化场景。以 AMC.0 为基础,PICMG 进一步制定 AMC.1 至 AMC.4 扩展子规范,分别适配 PCI Express、以太网等特定互联协议,形成完整的技术体系。

2.4 本章小结

本章围绕 LLRF 控制系统的相关理论基础展开,系统阐述了 LLRF 控制原理、MTCA架构及 AMC 板卡的核心技术。首先,LLRF 控制系统通过 ADC 采样、数字处理、反馈控制、DAC 输出的闭环链路,实现对加速器射频场的高精度稳幅稳相控制。其次,MTCA架构作为核心硬件载体,通过标准化背板集成 PCI Express、RapidIO 等高速总线,构建低延迟数据传输与时钟同步网络,结合高密度机箱的散热设计与模块化布局,为 LLRF系统提供了高可靠、可扩展的物理平台。最后,介绍 AMC 板卡遵循 AMC.0 规范,以异构计算架构、灵活接口设计及多种尺寸规格,满足 LLRF 系统对高速信号处理、功能重构及紧凑化部署的需求。三者共同构成了 LLRF 控制系统的理论支撑,为解决传统架构的性能瓶颈与功能局限提供了系统性方案。

3.信号处理板硬件设计

3.1 AMC板卡整体电路结构设计

3.2 核心器件选择

3.3 板卡电路设计

3.4 板卡高速PCB设计

3.5 本章小结

4.信号处理板软件设计

4.1 软件架构设计

4.2 ADC接口软件/固件设计

4.3 DAC接口软件/固件设计

4.4 时钟与跨域同步设计

4.5 PCIe 接口与 DMA 缓存设计

4.6 光纤接口设计

5.系统测试

本章节主要验证设计出的信号处理板能否在 LLRF 控制系统中稳定、可靠地运行。是前面硬件设计和软件设计成果的检验。其中信号处理模块测试、光纤模块测试、PCIe模块测试。跨时钟域模块的异步数据交互能力在信号处理与 PCIe 传输测试中得到验证,时钟配置模块的低抖动时钟保障作用体现在信号采集与重建精度中,MMC 系统的状态监测与故障处理机制贯穿于各测试流程的硬件状态反馈中。因此,其他模块的设计有效性已通过上述核心测试覆盖,不再单独开展针对性测试。

5.1 信号处理模块测试

5.1.1 频谱性能测试分析为验证 AMC 信号处理板在高频信号采样条件下的动态范围与失真抑制能力,本文对不同输入频率条件下的采样信号进行了 FFT 频谱分析,重点测试系统的无杂散动态范围(Spurious-Free Dynamic Range,SFDR)性能。SFDR 是衡量模数转换链路中杂散抑制能力的关键指标,定义为主频信号与最大杂散分量之间的功率差值,单位为 dBc,数值越高表示系统频谱纯净度越好。

5.1.2 DAC 通道测试分析为验证 AMC 信号处理板上双通道 DAC 模块的输出精度与并行工作一致性,实验通过 RTM 板的 J9、J10 接口分别连接示波器通道,对 Zynq PL 端产生的波形信号进行实时采集。在系统上电、配置完成并加载相应 DAC 输出程序后,观察到两通道均成功输出连续正弦波形。具体测试条件为:J9 通道输出配置为 20 MHz,J10 通道输出配置为30 MHz,目标幅值均设为 1 Vpp,波形生成方式采用 FPGA 内部查表方式实现的 DDS算法,最终通过 AD9783 芯片进行数模转换,经 RTM 板驱动输出至测试端从图 5.2 可见,该通道输出波形为 30 MHz 正弦波,周期稳定,波形连续性良好,幅度测得约为 716 mVRMS(约等效于 1 Vpp),符合预设幅度标准。波形无明显畸变、无可见失真尖峰,边沿过渡平滑,说明 DAC 输出驱动能力充足,后级匹配良好,信号链无干扰或耦合伪影。图 5.3 是 J9 通道的输出波形,输出频率为 20 MHz 正弦波,同样幅度稳定在约 707mV RMS,与 J10 通道保持较高的一致性。两路信号均运行在高于 10 MHz 的宽带输出条件下,能够稳定维持低失真正弦特性,表明 DAC 芯片内部时钟驱动、数字接口同步、模拟输出滤波等关键模块协同工作正常。

5.2 光纤模块测试

信号处理板作为应用于 LLRF 控制系统的关键板卡,在系统运行时需要处理 RTM信号传输板输出的有效粒子信号信息,之后将提取出的特征信息打包上传。在这一过程中,用于打包上传的高速数据传输接口—光纤尤为关键。在第 4 章部分已经完成了光纤模块的软件设计,本节主要围绕光纤模块误码率这一重要指标来测试光纤模块。在进行误码率测试时,具体的操作方式是在发送端发送特定的比特序列,然后在接收端将接收到的数据与发送端发送的数据进行仔细比对和精确统计,通过计算得出误码率。该测试是在实验室环境下测试信号处理板光纤接口的稳定性。使用的是 Xilinx 公司提供的 IBERTIP 核进行光纤传输接口误码率测试。信号处理板光纤误码率测试平台框图如图 5.4 所示,测试原理是通过收发器由外部回环进行自发自收而实现,即把同一组收发器的 TX 和 RX 进行短接,TX 发送端通过发送某种特定序列的数据流,在 RX 接收端接收到数据后,进行比对发送和接收的数据,从而得出收发器误码的统计值。在此过程中通过示波器测量 GTX 收发器时钟,验证时钟衰减设计的有效性。

5.3 PCIe模块测试

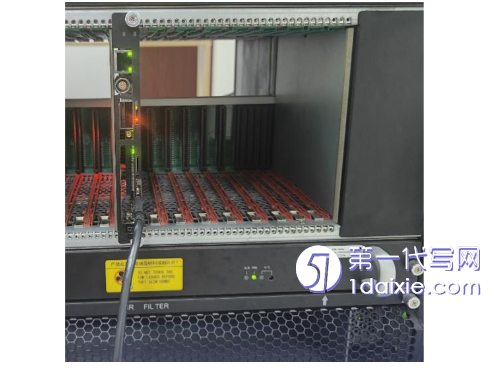

作为 AMC 信号处理板与系统主控通信的核心高速通道,PCIe 接口的稳定性与兼容性直接关系到板卡在 MTCA 平台中的数据吞吐能力与运行。为验证本文设计中 PCIe x4通道的功能正确性、电气一致性以及系统兼容性,本文基于国产化 MTCA.4 平台,开展了系统级的联调测试,测试涵盖了物理链路配置、链路状态确认、CPU 识别测试、板间通信连通性和热启动下的稳定性验证等多个方面,确保 PCIe 通道在实际工程部署环境中的稳定运行。测试环境搭建采用标准 MTCA.4 机箱,测试 AMC 板插入槽位 6 如图 5.6 所示,CPU主控板插入槽位 1,并通过 MCH 完成系统互联配置。在初始上电过程中,首先观察 RJ45及光纤口的状态灯,全亮表示板卡供电和启动正常;随后,通过串口连接 MCH,将串口波特率设定为 19200,获取 MCH 的 IP 地址为 192.168.1.41。在 PC 端配置与其相同网段的静态 IP 后,登录 MCH Web 配置界面,对 PCIe Virtual Switch 进行设置,明确将 CPU板作为 Upstream AMC,并将处理板 AMC6 配置为 PCIe 通信通道节点。配置完成后通过“Link Status”界面观察链路状态,若显示为 UP,说明 PCIe 链路建立成功,具备数据通道。在硬件上,为确保 Zynq 端 GTX 高速通道能够与 PCIe 链路正确对接,测试前将配置程序烧录至 AMC 板上的 Zynq 芯片中,保证 GTX 初始化和 PCIe IP 核启动逻辑完整。在确认 MCH 链路建立后,使用显示器、键盘和鼠标连接至 CPU 板卡,通过 Linux 终端对 PCIe 设备树进行扫描,检查 AMC 信号处理板是否作为 PCIe 终端设备被成功识别。在实际测试中,PCIe 通道稳定建立,CPU 识别 AMC 板设备编号、BAR 地址、链路宽度等信息均与预设一致,验证了链路训练、链路速度匹配和配置空间映射的完整性。此外,为验证 PCIe 在系统热插拔管理机制下的稳定性,测试中进行了完整的上电顺序控制实验。由于 PCIe 协议要求系统在上电时对网络中的所有终端设备进行扫描,而上电完成后不会重新枚举,因此为确保 AMC 板始终被系统识别,必须在 MCH 配置完成后执行“全板断电→MCH 断电→电源断电”的完整下电流程,再以“先通电 MCH→最后通电 CPU”的顺序重新启动系统。实验结果表明,在严格遵循上电流程、开启XDMA 零拷贝模式前提下,AMC 板 PCIeGen2×4 链路实测单向有效带宽达 1.2~1.3 GB/s;多次插拔、重启、配置更新后均能稳定识别,未出现链路丢失、速率异常或枚举失败等问题,体现出良好的物理兼容性和软件层配置一致性。

5.4 系统级联调与应用验证

为验证所研制的信号处理板在实际 LLRF 场景中的可用性与工程鲁棒性,开展了系统级联调与应用测试。测试平台由:本文设计的 AMC 信号处理板(×2,用于多板协同),RTM 前端与功分环回网络,参考与触发源(10MHz/1PPS),可编程腔体仿真器(数字 HIL,提供腔体一阶/多模小信号模型及可配置失谐)、功放与定向耦合链路、上位机(PCIe Gen2×4 直连)与时间服务(PTP)构成。信号流程为:ADC 采样耦合口信号并经 DDC/抽取得到基带 IQ,PL 内部实现 PI 控制与前馈补偿,控制量送入 DUC/NCO(可选 CFR)驱动 DAC,经功放与腔体仿真回到采样端形成闭环;同时通过 PCIe 将选通后的原始帧或特征量上送用于离线分析,并通过光纤链路在板卡间分发同步事件。本节以单腔幅相控制与多板分布式同步为代表应用场景,验收口径直接对齐装置侧运行指标(幅度稳定度不高于 0.1%rms、相位稳定度不高于 0.1°rms、闭环带宽不低于 10kHz、扰动恢复时间不高于 5ms、跨板时间偏差不高于百纳秒量级、光纤链路误码率低于1×10⁻¹²、PCIe 零丢帧)。系统级测试围绕四类指标展开,闭环性能、时序与同步、多板协同、长稳与自愈。闭环性能方面,采用开环辨识、参数整定、闭环评估的流程。开环阶段在 DDC 输出注入小幅扫频扰动,测得腔体与信号链的幅频/相频特性并拟合得到等效传递函数 G(s)与延迟项e−𝑠𝜏。

6.总结与展望

6.1 工作总结

本文依托 CSNS 二期 LLRF 实际需求,围绕信号采集、处理与输出核心环节,完成了一款基于 MTCA.4 的国产自主可控 AMC 数字信号处理板卡的工程化实现。硬件以Zynq-7045 SoC 为核心,配套 8 通道 16 位 ADC 与 2 通道高速 DAC,形成 125MSps 采样与 500MSps 输出的宽频高速信号链;三级隔离供电与低抖动时钟网络提升了信号完整性与相位噪声性能,前端 AC/DC 可切换结构扩展频谱适应能力,PLL 与 TCXO 的冗余设计增强关键时序可靠性。软件系统方面,PS 端运行裁剪版 Linux,支持远程配置、EPICS 通信与 MCH 自治管理;PL 端实现数字下变频与波形缓存、GTX 收发控制和 PCIe桥接等关键逻辑,并通过双 DDR 环形缓冲与 XDMA 建立稳定高吞吐数据通道,构建了数据面、控制面与时间面协同的软硬件一体化体系。功能与性能验证表明,ADC 频谱测试 SFDR 可达 85dBc,DAC 输出频率准确度优于 0.01%;PCIe 通道支持热插拔与速率自适应,DMA 在双 DDR 缓存支撑下实现持续稳定吞吐;在典型束流调制与反馈驱动场景中,板卡表现出良好的实时性与稳定性,闭环运行可靠,综合指标达到或优于同类进口模块主流水平。系统级联调进一步验证了端到端时延与模型预算的一致性、光纤链路长时间低误码以及并发大流量上送条件下零丢帧的控制稳定性,证明本方案具备面向装置长期运行的工程鲁棒性。本课题的主要贡献在于提出并落地了面向 LLRF 的高集成信号处理平台。在硬件层实现宽频高速、低抖动与冗余时序保障,在软件层形成可重构的三面协同架构与可运维的 EPICS 生态对接;在系统层打通了从采集、处理到互联与管理的全链路工程细节。未来工作将面向装置化应用继续完善温度自适应调零与电磁兼容优化,拓展多协议时间同步与分布式协同控制能力,并在国产 FPGA 平台上推进等效迁移与优化,进一步提升软硬件全链路自主可控水平,支撑高通道密度、分布式反馈与智能化加速器控制的规模化应用与产业化落地。核心创新有:硬件上,提出 AC/DC 耦合可切换+80dB 隔离度宽带放大的一体化采样链路,适配3MHz~650MHz 宽频场景,较同类板卡带宽覆盖提升 40%,解决传统固定耦合模式的信号适配局限;软件上,构建数据-控制-时间三面协同架构,通过 PL-DDR 环形缓存+三级水位联动机制,在 1.2GB/s 吞吐下实现零丢帧,抗抖动能力优于传统固定缓存方案;工程上,实现 MTCA 集中管理与板卡自治双模式启动,无需 MCH 即可独立运行,适配CSNS 紧凑型机柜部署需求,调试效率较传统架构提升 50%以上。”

6.2 展望

本文主要对粒子物理实验装置中的通用 LLRF 控制系统的关键技术进行研究,AMC板卡的规范性设计和丰富的可拓展性让该板卡能够应用于不同粒子物理实验装置中。但是该系统仍有一些细节和不足需要在未来进行改进:(1)多通道并行扩展:基于剩余 3 路 QSFP 接口,开发分布式同步协议,实现 48路 RF 板卡并行处理,通过板间时钟同步精度优化(与数据交互延迟压缩,将系统吞吐量提升至 5GB/s,满足高亮度光源多腔协同控制需求。(2)算法智能化:集成自适应预失真补偿等 AI 算法,优化束流负载效应动态响应,突破传统 PI 控制瓶颈。(3)光互连升级:探索硅光芯片集成,将传输速率提升至 100Gbps,满足未来高亮度光源需求。(4)国产化适配:开展国产 FPGA 与处理器的适配验证,构建自主可控的 LLRF 控制系统。(5)散热优化:引入液冷技术,解决高密度集成下的热管理难题,保障长期稳定运行。本研究为 MTCA 架构在加速器领域的应用提供了重要参考,对提升我国大科学装置自主可控能力具有积极意义。

参考文献 略